- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

เทคโนโลยีการแกะสลักแบบคัดเลือก SiGe และ Si

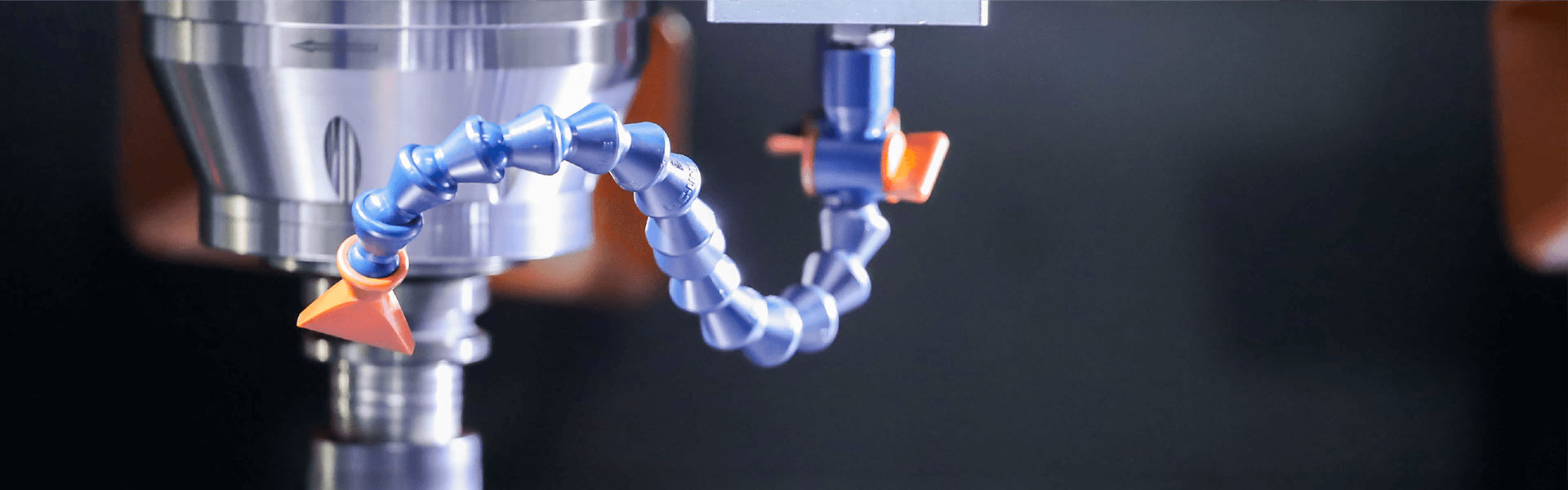

Gate-All-Around FET (GAAFET) ซึ่งเป็นสถาปัตยกรรมทรานซิสเตอร์เจเนอเรชันถัดไปที่พร้อมจะเข้ามาแทนที่ FinFET ได้รับความสนใจอย่างมากจากความสามารถในการควบคุมไฟฟ้าสถิตที่เหนือกว่าและเพิ่มประสิทธิภาพในขนาดที่เล็กลง ขั้นตอนที่สำคัญในการสร้าง GAAFET ชนิด n เกี่ยวข้องกับการเลือกสรรสูงการแกะสลักของ SiGe:Si จะเรียงตัวกันก่อนการสะสมของตัวเว้นระยะภายใน ทำให้เกิดแผ่นนาโนซิลิคอนและช่องปล่อย

บทความนี้เจาะลึกการคัดเลือกเทคโนโลยีการแกะสลักมีส่วนร่วมในกระบวนการนี้และแนะนำวิธีการแกะสลักแบบใหม่สองวิธี ได้แก่ การกัดแบบไร้พลาสมาด้วยก๊าซออกซิเดชันสูง และการกัดแบบอะตอมมิกเลเยอร์ (ALE) ซึ่งนำเสนอโซลูชั่นใหม่เพื่อให้ได้ความแม่นยำสูงและการเลือกสรรในการกัด SiGe

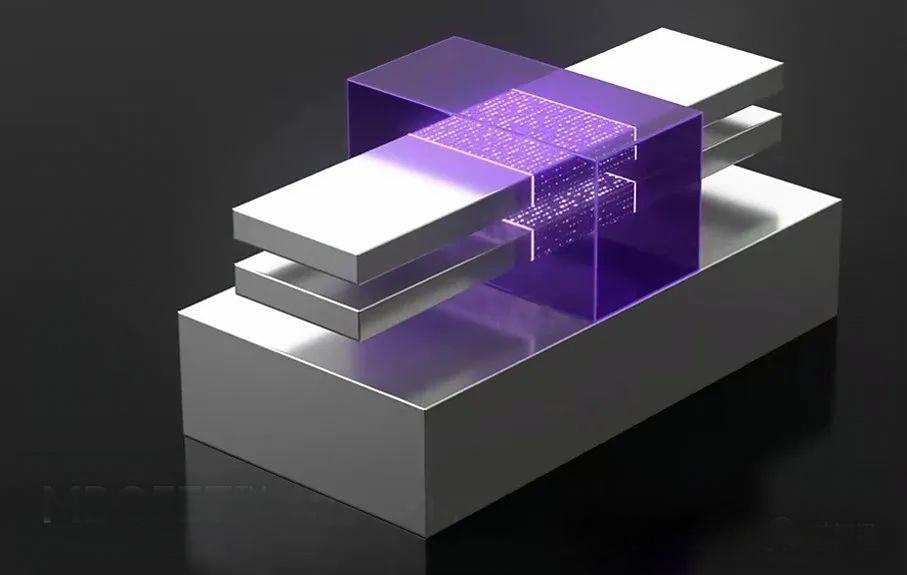

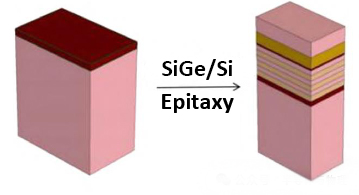

เลเยอร์ SiGe Superlattice ในโครงสร้าง GAA

ในการออกแบบ GAAFET จะมีการสลับเลเยอร์ของ Si และ SiGe เพื่อเพิ่มประสิทธิภาพของอุปกรณ์ปลูกแบบ epitaxly บนพื้นผิวซิลิกอนทำให้เกิดโครงสร้างหลายชั้นที่เรียกว่าซูเปอร์แลตทิซ ชั้น SiGe เหล่านี้ไม่เพียงแต่ปรับความเข้มข้นของตัวพา แต่ยังปรับปรุงการเคลื่อนที่ของอิเล็กตรอนด้วยการแนะนำความเครียด อย่างไรก็ตาม ในขั้นตอนกระบวนการต่อๆ ไป ชั้น SiGe เหล่านี้จำเป็นต้องถูกเอาออกอย่างแม่นยำ ในขณะที่ยังคงชั้นซิลิคอนไว้ ซึ่งต้องใช้เทคโนโลยีการกัดแบบคัดเลือกสูง

วิธีการแกะสลักแบบเลือกสรรของ SiGe

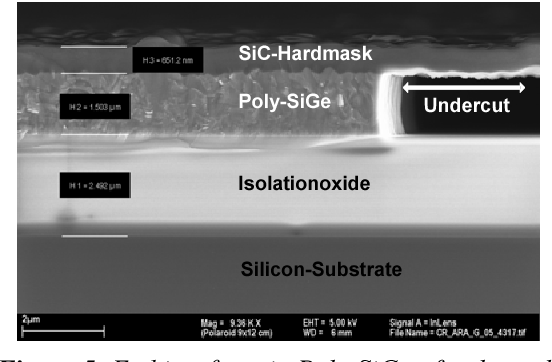

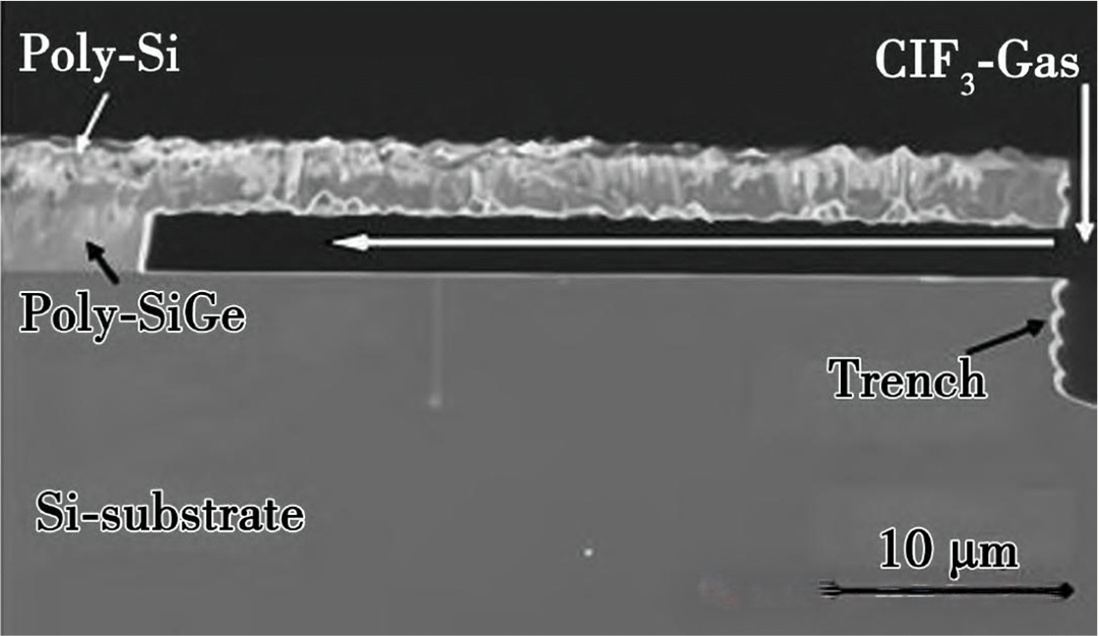

การกัดแบบไร้พลาสมาด้วยแก๊สออกซิเดชันสูง

การเลือกก๊าซ ClF3: วิธีการกัดกรดนี้ใช้ก๊าซออกซิเดชั่นสูงโดยมีค่าหัวกะทิสูง เช่น ClF3 เพื่อให้ได้อัตราส่วนหัวกะทิของ SiGe:Si ที่ 1000-5000 สามารถทำได้ที่อุณหภูมิห้องโดยไม่ทำให้พลาสมาเสียหาย

ประสิทธิภาพที่อุณหภูมิต่ำ: อุณหภูมิที่เหมาะสมที่สุดคือประมาณ 30°C ทำให้มีการเลือกสรรสูงภายใต้สภาวะอุณหภูมิต่ำ หลีกเลี่ยงการเพิ่มงบประมาณด้านความร้อนเพิ่มเติม ซึ่งเป็นสิ่งสำคัญสำหรับการรักษาประสิทธิภาพของอุปกรณ์

สภาพแวดล้อมที่แห้ง: โดยรวมกระบวนการแกะสลักดำเนินการภายใต้สภาวะที่แห้งสนิท ช่วยลดความเสี่ยงของการยึดเกาะของโครงสร้าง

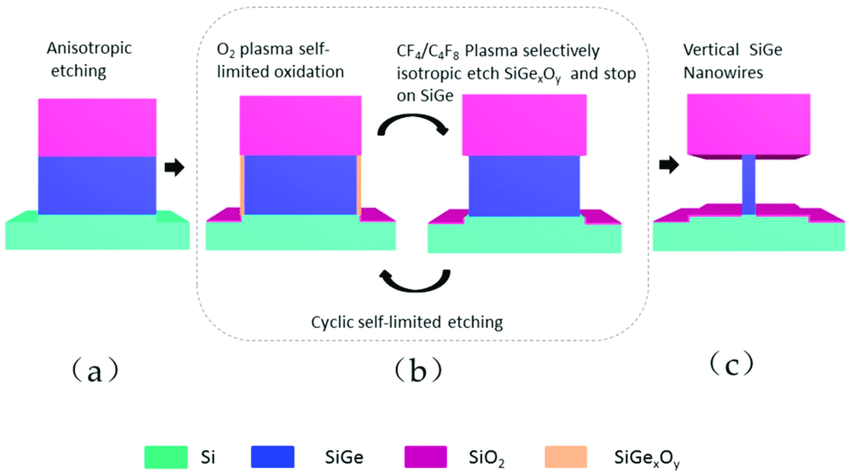

การแกะสลักชั้นอะตอม (ALE)

ลักษณะการจำกัดตัวเอง: ALE เป็นวงจรสองขั้นตอนเทคโนโลยีการแกะสลักโดยที่พื้นผิวของวัสดุที่จะแกะสลักได้รับการแก้ไขในขั้นแรก จากนั้นชั้นที่แก้ไขจะถูกลบออกโดยไม่กระทบต่อชิ้นส่วนที่ไม่มีการดัดแปลง แต่ละขั้นตอนมีการจำกัดตัวเอง จึงรับประกันความแม่นยำถึงระดับการกำจัดชั้นอะตอมเพียงไม่กี่ชั้นในแต่ละครั้ง

การแกะสลักแบบวน: สองขั้นตอนข้างต้นจะถูกวนซ้ำ ๆ จนกว่าจะได้ความลึกของการแกะสลักตามที่ต้องการ กระบวนการนี้ช่วยให้ ALE บรรลุเป้าหมายได้การแกะสลักที่มีความแม่นยำระดับอะตอมในช่องเล็กๆ บนผนังด้านใน

พวกเราที่ Semicorex เชี่ยวชาญด้านโซลูชันกราไฟท์เคลือบ SiC/TaCใช้ในกระบวนการแกะสลักในการผลิตเซมิคอนดักเตอร์ หากคุณมีข้อสงสัยหรือต้องการรายละเอียดเพิ่มเติม โปรดอย่าลังเลที่จะติดต่อเรา

โทรศัพท์ติดต่อ: +86-13567891907

อีเมล์: sales@semicorex.com